外媒 eNewsEurope 报道,英特尔 (Intel) 和台积电将在国际电子元件会议 (IEDM) 公布垂直堆叠式 (CFET) 场效晶体管进展,使 CFET 成为十年内最可能接替闸极全环电晶 (GAA ) 晶体管的下一代先进制程。

英特尔的 GAA 设计堆叠式 CFET 晶体管架构是在 imec 的帮助下开发的,设计旨在增加晶体管密度,通过将 n 和 p 两种 MOS 器件相互堆叠在一起,并允许堆叠 8 个纳米片(RibbonFET 使用的 4 个纳米片的两倍)来实现更高的密度。目前,英特尔正在研究两种类型的 CFET,包括单片式和顺序式,但尚未确定最终采用哪一种,或者是否还会有其他类型的设计出现,未来应该会有更多细节信息公布。

此前在 2021 年的「英特尔加速创新:制程工艺和封装技术线上发布会」上,英特尔已经确认了 RibbonFET 将成历史,在其 20A 工艺上,将引入采用 Gate All Around(GAA)设计的 RibbonFET 晶体管架构,以取代自 2011 年推出的 FinFET 晶体管架构。新技术将加快了晶体管开关速度,同时实现与多鳍结构相同的驱动电流,但占用的空间更小。

虽然,大多数早期研究以学术界为主,但英特尔和台积电等半导体企业现在已经开始这一领域的研发,借此积极探索这种下一代先进晶体管技术。

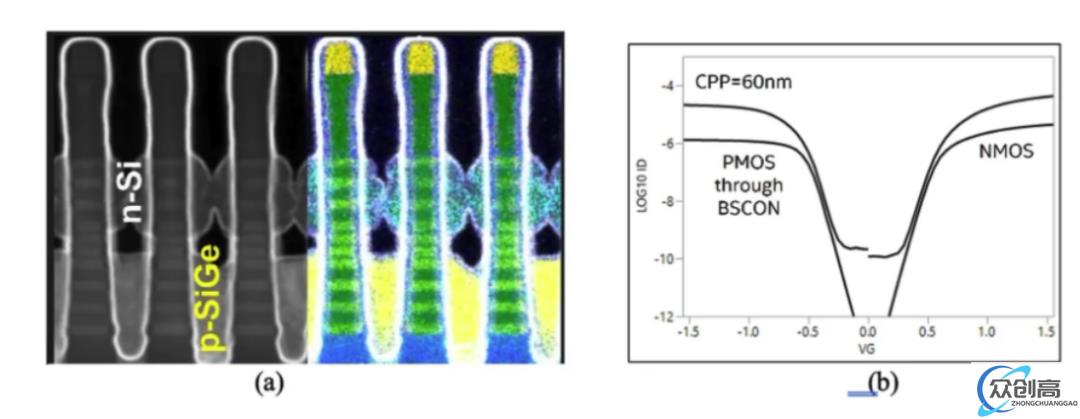

英特尔表示,研究员建构一个单片 3D CFET,含三个 n-FET 纳米片,层叠在三个 p-FET 纳米片上,保持 30 纳米垂直间隙,取名为采用电源通孔和直接背面元件触点 60 纳米闸极间距堆叠式 CMOS 逆变器示范,描述 60 纳米闸极间距利用 CFET 功能逆变器测试电路。采垂直分层双电源漏外延和双金属闸极堆叠,结合 PowerVia 背后供电。

为了不被对手超越,台积电也会展示如何达成 CFET。此为客制逻辑芯片,有 48 纳米栅极间距,专注放在 p 型晶体管上的分层 n 型纳米片晶体管,拥有跨越六个等级的卓越开关电流比。

台积电 CFET 晶体管已证明耐用性超过 90%,且成功通过测试。虽然台积电承认需要研究更多,才能充分利用 CFET 技术,但是实现 CFET 晶体管技术的关键。CFET 明显转变晶体管设计,允许垂直堆叠两个晶体管安装至一个晶体管面积内,增加晶体管密度,且不仅为提高空间使用提供解决方案,还促进更精简 CMOS 逻辑电路布局,有利提高设计效率。

CFET 既有结构可能会减少寄生效应,逐渐提高性能和功率效率。结合适应性设计与背面供电等创新,可简化制程复杂性,使 CFET 成为晶体管领域愿景。英特尔和台积电的努力,也突显 CFET 技术对半导体产业未来的重要性。

复旦大学研发出异质 CFET 技术

复旦大学研究团队:周鹏教授、包文中研究员及万景研究员,创新地提出了硅基二维异质集成叠层晶体管。该技术将新型二维原子晶体引入传统的硅基芯片制造流程,绕过 EUV 光刻工艺,实现了晶圆级异质 CFET 技术。

该团队利用硅基集成电路的成熟后端工艺,将二硫化钼 (MoS2) 三维堆叠在传统的硅基芯片上,形成 p 型硅-n 型二硫化钼的异质互补 CFET 结构。结果证明,在相同的工艺节点下实现了器件集成密度翻倍,并获得了卓越的电学性能。

简单来说,就是该团队研发出的异质 CFET 技术,是设计了一种晶圆级硅基二维互补叠层晶体管,不需要用到 EUV,也可以实现晶体管密度翻倍。

随着芯片工艺制程不断进步,就需要尺寸更小、功能更强大的晶体管,同时,会让制程微缩到一定程度,原本的晶体管技术就会出现静电、漏电问题。因此,晶体管技术也随着工艺迭代加快升级,而升级的重点在于提升静电性能、控制漏电流。

比如,22nm 工艺之后,FinFET 取代 MOSFE 工艺,3nm 工艺时代,GAAFET 取代 FinFET 工艺,再先进的工艺(比如 2nm 以下),CFET 将取代 GAAFET 工艺。因此,CFET 是 GAAFET 工艺的迭代技术,也称之为全硅基 CFET 技术。

这对于国内自主发展新型集成电路技术具有重要意义。毕竟,在中企无法获得先进的 EUV 光刻机下,该技术给予了另一种可行性研究方向。如果一旦成功应用,那么将会绕过 EUV 光刻机的问题,制造出更先进的芯片。

以及 CFET 属于下一代晶体管技术,是未来发展的重点,该技术的研发有利于我们取得先机。特别是在关键技术专利方面,先取得更多的研究成果与专利,对于后期芯片制程的发展是更有利的。