提高汽车电气化和自动驾驶的一个主要方面是先进驾驶辅助系统(ADAS)的普及。如今,这些系统正迅速应用于市场上几乎所有的车辆,而且随着技术的成熟,这一趋势只会持续下去。然而,随着技术的发展,ADAS设计人员面临的硬件挑战变得越来越复杂。在本文中,我们将介绍ADAS的硬件需求,FPGA如何填补这些空白,以及为什么eFPGA IP将成为下一个ADAS硬件趋势。

ADAS的硬件要求

ADAS在现代汽车中的发展给底层硬件带来了一些严峻的挑战。在像ADAS这样的关键任务应用中,最重要的目标是确保车辆乘员的安全。这个目标要求系统准确、可靠和实时地工作(即低延迟)。同时,这些系统需要在尽可能低的功耗下运行,以保持电池寿命并延长电动汽车(Electric Vehicle)的续航里程。

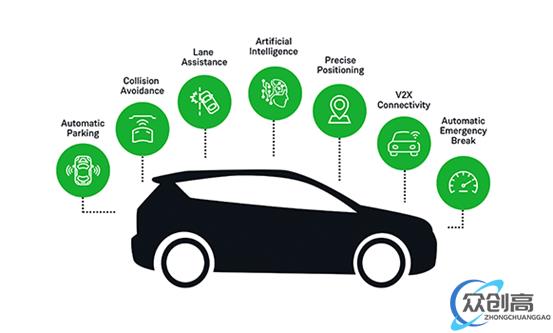

图:ADAS给计算硬件造成了巨大压力

平衡这些需求对ADAS来说是一个巨大的挑战,因为系统往往依赖于大量的数据和计算密集型的任务,如机器学习算法。因此,ADAS硬件必须获取数据,通过传感器融合汇集数据,运行机器学习算法,然后采取行动——所有的都需要实时运行,并以最低的功耗预算——这显然不是一件容易的事。

汽车设计人员需要一个灵活且可扩展的硬件平台来满足快速发展的规格变化,这进一步加剧了这一挑战。

硬件加速和FPGA

为了解决ADAS硬件面临的严峻挑战,设计人员正在采用专用硬件加速器来提高性能,而不是传统的基于CPU的架构。从比较常规的计算资源(如CPU或GPU)转移,通过专用硬件加速器为特定应用程序提供了更好的性能和能效。基于在此范围内,选择通常介于FPGA和ASIC之间,FPGA提供最大的灵活性,ASIC提供最高的性能。

FPGA的一个关键特性是FPGA能够提供高级别的并行性,同时仍然可以针对特定的工作负载进行编程。结果表明,FPGA在工作负载加速方面提供了显著的价值,特别是在性能和延迟作为关键的情况下。此外,与比较常规的CPU和基于GPU的系统相比,FPGA可以给需要加速的工作负载提供每瓦最佳的性能,从而帮助系统平衡性能和功率效率之间的权衡。

同样重要的是,由于FPGA可编程特性,其在可扩展性方面比ASIC更具优势。这种适应性在如ADAS等底层算法瞬息万变的机器学习系统中尤为重要。此外,ASIC的规格必须提前几年定义,而FPGA可以在一分钟内更新和重新编程。此功能使基于FPGA 的ADAS系统能够提供ASIC根本无法实现的可扩展性和多功能性。

由于这些原因以及更多的原因,目前汽车中已经搭载了超过2.5亿颗FPGA,其中超过7500万颗用于ADAS应用。

行业趋势:用于ADAS的eFPGA

尽管硬件加速功能强大,但像FPGA和ASIC等器件通常仍无法完全独自运行。今天的ADAS解决方案需要将硬件加速器与CPU集成在一起,其目的是在系统级别处理许多通用型和组织型任务。正是由于这个原因,异构计算平台(如异构SoC)已经成为加速和ADAS平台中最常见的平台之一。

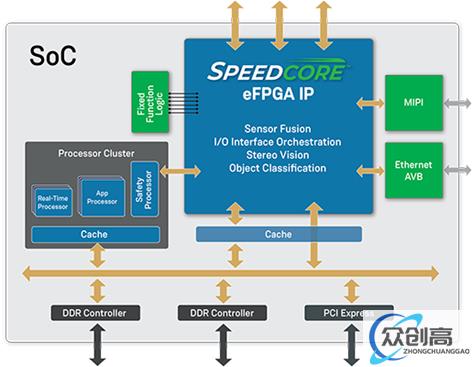

图:Achronix的Speedcore IP这样的eFPGA技术可以与CPU资源紧密耦合

因此,我们相信ADAS计算的下一个主要趋势将是嵌入式FPGA(即eFPGA)IP在定制ASIC中的兴起。借助eFPGA IP,设计人员能够利用FPGA技术的优势,同时将其硬件加速与其他ASIC子系统(如CPU和I/O接口)紧密耦合。通过将FPGA与CPU一起嵌入到定制SoC中,与分立式FPGA解决方案相比,eFPGA IP可显著节省成本、功耗和空间。

具体来说,我们的评估表明,与基于FPGA的独立系统相比,eFPGA IP集成可以帮助设计人员节省90%的成本、降低75%的功耗、延迟改善100倍、接口带宽增加10倍。因此,ADAS将在不久的将来逐步采用基于eFPGA技术的异构解决方案。

Achronix的行业角色

如今Achronix是唯一一家同时大批量生产独立FPGA芯片和eFPGA IP解决方案的公司。得益于我们的Speedcore eFPGA IP等旗舰产品,迄今为止,我们已经在多个行业领域授权了超过1500万个基于eFPGA的产品。随着对ADAS计算需求的不断增长和演进,我们认为有能力支持这些变化并赋能下一代计算平台。