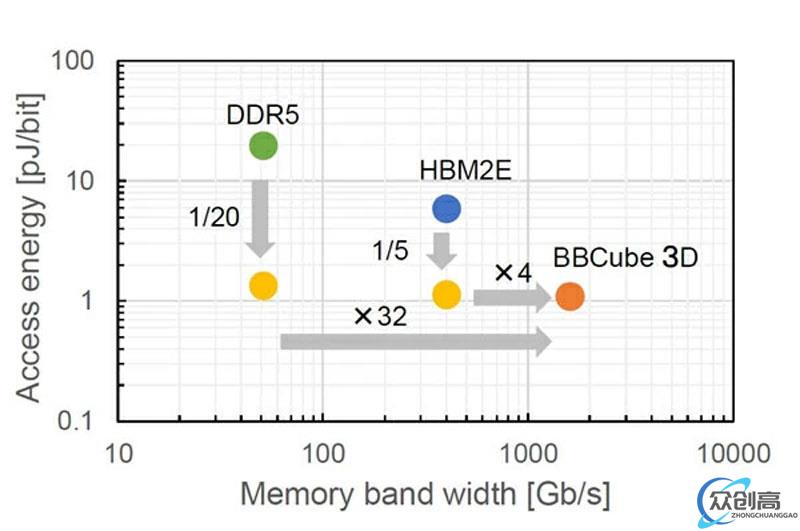

IT之家 7 月 7 日消息,来自东京工业大学的科研团队近日研发出可堆叠内存,其传输速度是 HBM2E 内存的 4 倍,功耗仅为五分之一。

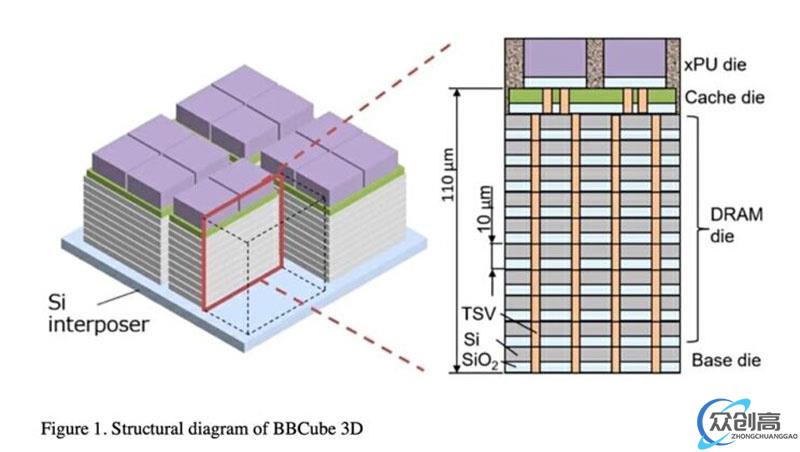

科研团队将其称为 BBCube,最大的亮点在于去除了传统内存的逐层焊接晶体布局。

科研团队在 2023 年 6 月举行的 VLSI IEEE Symposium 2023 大会上得到了同行论证,不仅提出了这一新概念,还详细描述了生产这种存储器的技术流程。

IT之家注:高带宽存储器(HBM)是三星电子、超微半导体和 SK 海力士发起的一种基于 3D 堆栈工艺的高性能 DRAM,适用于高存储器带宽需求的应用场合,像是图形处理器、网络交换及转发设备等。

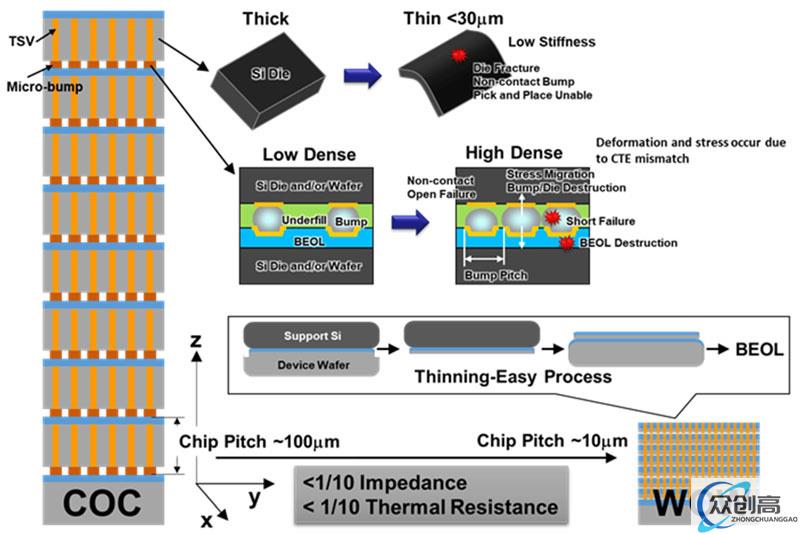

生产 HBM 内存的现有方法限制了其功能,堆叠中的每一层(DRAM 芯片)不能制造得比特定规格更薄,并且层之间的球接触(ball contacts)数量不能增加超过特定值,否则存在机械损坏和短路的风险。

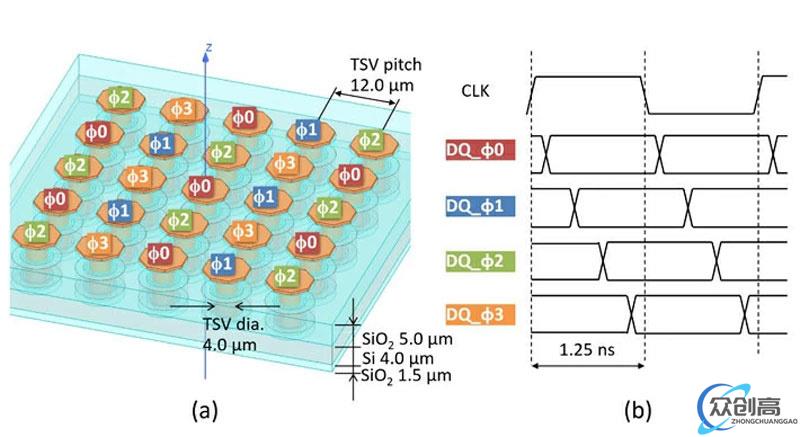

科研团队提议在 DRAM 封装过程中去除球接触,可以让芯片变得更薄,降低每一层的机械应力,缩短 TSV 的过孔线。

研究团队负责人 Takayuki Ohba 教授表示:“BBCube 3D 有潜力实现每秒 1.6 TB 的吞吐量,比 DDR5 快 30 倍,比 HBM2E 快四倍。”