晶片是用来干嘛的?为什么日常生活中会用到晶片呢?晶片这么重要吗?晶圆又是什么呢?

在过去,需要将电晶体、二极体、电阻、电容等电子元件焊接成电路,并将这个能执行简单逻辑运算的电路装置在电子产品上,才能够让电子产品顺利运作,然而手工焊接不仅成本高且耗时,效果也不理想。后来德州仪器的工程师–杰克·基尔比,便想到如果能够事先设计好电路图,然后照电路图将所有电子元件整合在矽晶元上,便能解决手工焊接的难题,而这就是全世界第一个“集成电路”也就是我们常听到的IC(IntegratedCircuit)的由来。

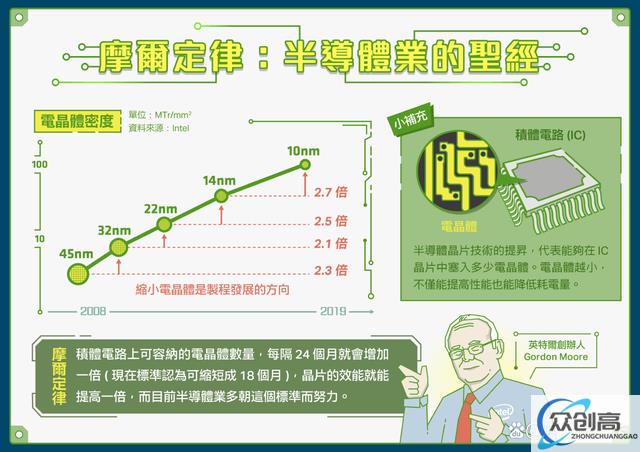

集成电路发明后,技术也开始高速发展,一个晶片从原本仅能塞不到五个电晶体,到后来可以塞下数亿个电晶体。而电晶体缩得越小,除了更低的能耗、延迟以及更高的效能外,也让晶片随之缩小,电子产品也能越来越小。如今这些优点正反应在电子产品上,让生活越来越方便。

晶圆代工是什么?

晶圆代工(Foundry)是半导体产业的一种商业模式,指接受其他无厂半导体公司(Fabless)委托、专门从事晶圆成品的加工而制造集成电路,并不自行从事产品设计与后端销售。下面带你认识晶圆代工的流程。

晶圆代工流程一:矽晶圆生产

晶片最伟大的贡献,莫过于将原本仅能执行0和1的逻辑运算(注)的电晶体,集合在一起形成具有强大处理能力的运算中枢,而连结这些电晶体的基板就是“矽”这个元素。

之所以会选择“矽”作为IC的主要原料,是因为矽在自然界中属于“半导体”,也就是导电性介于导体与绝缘体的存在,可以借由加入杂质,来调整半导体的导电性,进而控制电流是否流通,达到讯号切换的功能,换句话说就是让晶片能够顺利执行0和1的运算,而能操控电子产品。

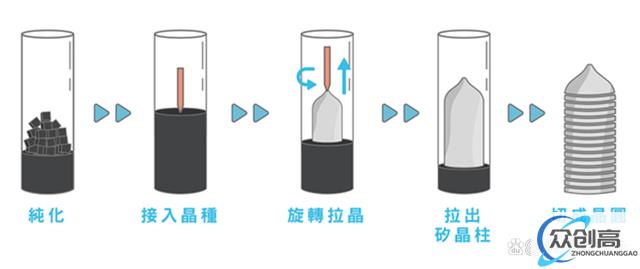

矽晶圆的制造流程简化来说就是将“矽”加工至可用来放置电子元件的“矽晶圆”:

纯化:矽的前身是石英砂,里面含有许多杂质,因此需要将其纯化,主要方式为将石英砂加入碳并加热还原成冶金级矽,随后将其丢入反应炉中与氯化氢以及氢气反应形成多晶矽。

拉晶:将多晶矽置入单晶炉中,透过加热处理、接入晶种(注1)后,就可以从中拉出半导体产业所需的“单晶矽柱”(矽晶柱),上面会有可摆放电晶体的“矽晶格”,也因此矽晶柱的品质掌控对于晶圆厂来说至关重要,拉晶的速度、温度的控制等等因子都有可能大大影响到最后的生产品质,而矽晶柱直径越大,拉晶也就越难。(注2)

注1:这边的晶种指的是一小块单晶矽,透过将晶种与熔融物接触并冷却凝固,借此形成大晶体,目的是让晶圆的原子排列能与晶种相同。

注2:单晶矽与多晶矽的区别:当矽原子以金刚石晶格排列成许多晶核时,如果各个晶核的晶面取向相同,则称为单晶矽,如果晶面取向不同,则称为多晶矽,在电学性质表现上,单晶矽优于多晶矽,因此在半导体产业中多采用单晶矽作为主要原料。

到这边为止,安置电子元件的基板–矽晶圆便完成了,而我们常在新闻中看到的8吋晶圆厂、12吋晶圆厂,指的其实就是矽晶圆的直径,不过,为什么要特地分成8吋、12吋或是X吋呢?

8吋晶圆 vs 12吋晶圆

其实关键就在于“生产成本”。简单的数学运算就可知道,一片12吋晶圆的表面积是一片8吋晶圆的2.25倍,也就是说在相同良率下,12吋晶圆厂的生产效率会是8吋晶圆厂的2.25倍,因此只要两种晶圆尺寸的生产成本差距在2.25倍以下的话,生产12吋晶圆便会比生产8吋晶圆来的有优势,故生产12吋晶圆其实是较为先进的技术。

12吋晶圆厂较有生产效率,为什么还要保留8吋晶圆厂?

前面提到,12吋晶圆厂的产量平均来说会是8吋晶圆厂的两倍多,因此在产能满载的前提下,12吋厂比较符合成本效益,然而对于某些客户集中在利基市场的厂商来说,不见得有足够的出货量去支撑12吋厂带来的额外产能,因此对这些厂商来说,也就没必要花更多的资金投资技术门槛更高的12吋厂。

8吋晶圆供不应求?

前面提到,某些产品市场规模不大,因此透过8吋或6吋晶圆厂来生产较有效率,相对的某些产品市场规模较大,因此产线通常都会分布在12吋晶圆厂。过去12吋晶圆厂主要拿来生产智能手机、笔记本电脑等有高阶运算需求的晶片,另一方面6吋、8吋晶圆厂则是用于生产物联网、车用元件等运算能力要求度不高的晶片。

由于过去12吋晶圆厂为市场主流,因此部分晶圆设备厂已经停止生产8吋晶圆厂的设备,而直接盖新的8吋厂又需要庞大的资金,对于大部分业者来说难以负荷。外加随着5G逐渐普及,物联网相关的晶片需求提升,因此8吋晶圆市场近期才会供不应求。

晶圆代工流程二:集成电路制造

回到IC制造的工作流程介绍,前面提及过去制作电路的方法,是将所有的电子元件手工连接起来,而相较之下集成电路的优势,就在于他是直接依照设计好的电路图,一口气将所有电子元件整合在一起。因此有个一致的标准,生产起来容易许多。

这两种电路制作模式的关键差异来自于“光学原理”。

简单来说,集成电路制造就是将从IC设计厂拿到的“电路设计图”透过光学成像的原理转移到“矽晶圆”上,最后依照设计图架构,在矽晶元上集成化所需的电子元件:

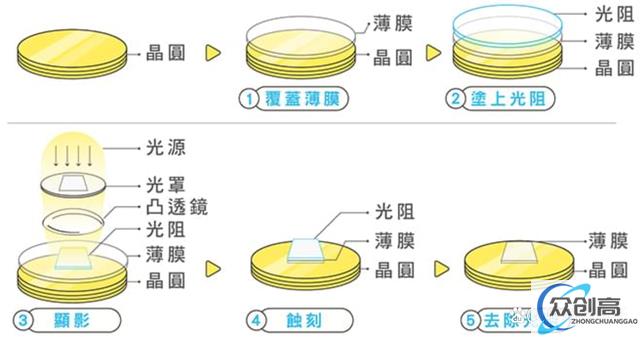

▲ 步骤1–镀上薄膜:于矽晶片表面镀上氧化层(或金属)。

▲ 步骤2–涂上光阻:于薄膜表面涂上光阻剂,该光阻剂曝光后化学结构会改变,变的相当易溶。

▲ 步骤3–显影:透过紫外光与凸透镜的聚光效果,将光罩上的电路图缩小并投影在光阻上。

▲ 步骤4–蚀刻:透过特殊化学溶液将被紫外光照射的光阻冲洗掉,接着再透过另一种化学溶液将步骤1的薄膜冲洗掉。

▲ 步骤5–光阻去除:接着最后一样以化学溶液将光阻去除。

注:实际过程相当复杂,需要堆叠许多不同材质的薄膜在特定的位置,因此需要好几十层的光罩并且不断重复上述步骤才能完成光刻制程,其他关于晶圆清洗、烘烤等步骤限于篇幅的关系,无法详细陈述。

在光刻制程结束后,紧接着就是注入杂质(磷原子与硼原子)到矽晶片(半导体)中控制其导电性,至此,构成集成电路所需的电晶体及相关的元件便已依照设计好的电路图在矽晶片上集成完毕,最后将铜倒入沟槽中形成电子接线,将数亿个电晶体串接起来后,近半个世纪以来不断推动科技进步的基石–集成电路便就此完成。

晶圆代工厂如何突破物理极限提升光刻技术?

相信有在关注台积电的人多少会看过跟上述类似的新闻,不过在探讨什么是摩尔定律、EUV等专有名词前,必须先了解光刻技术如何演进。

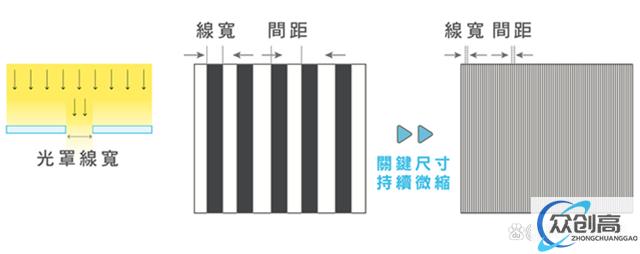

R=k1xNA是光学微影的分辨率公式,要想要有更好的成像品质,就必须要想办法提升分辨率,上述公式中,R代表至多可以曝出多小的线宽,越小则代表越精细、分辨率越高,能够执行越精细的光刻作业,代表光在真空中的波长,NA代表成像系统的数值孔径,k1则是一系数(受到许多制程相关因子影响)。

所以根据上述公式,要想提高分辨率,主要可以透过降低光源波长或是提高成像系统的数值孔径(注)来达成。

注:数值孔径(NA)没有单位。是用以衡量一个光学系统(镜头)能够收集的光的角度范围。

EUV是什么?

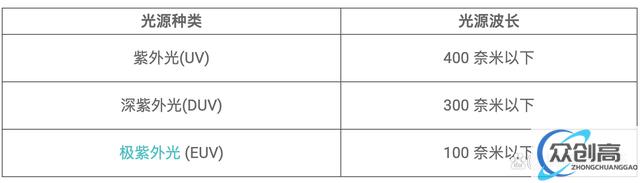

EUV微影技术的落实延续了摩尔定律的寿命,这里的EUV指的其实是一种紫外光源,跟过去光刻技术所采用的光源比起来,EUV的波长更短,因此有助于大幅提高分辨率。

摩尔定律是什么?

摩尔定律指的是集成电路上可容纳的电晶体数目,约每隔十八个月到两年增加一倍、性能也提升一倍,所以与其说是“定律”,其实它更像是一个用来描述集成电路产业演进轨迹的指标,而近几年许多新闻媒体之所以会认为摩尔定律快走到尽头,主要就是因为过去采用DUV光源的光刻技术在分辨率的提升上已经到达极限,换句话说就是媒体认为晶圆代工厂已经没有办法提供具有更高效能的晶片,这对晶圆代工厂甚至是对整个科技产业来说都会是相当大的冲击,也幸亏EUV微影技术的成功,才让摩尔定律得以延续。

晶圆几奈米是什么意思?

奈米是一公尺的负9次方,也就是头发厚度的10万分之一。而新闻上看到的“XX奈米”,则是指晶片上电晶体控制电流通过的“闸极长度”,长度越小,电晶体就越小,能塞进晶片的电晶体数量就越多,设备的效能也会相应提升。

而随着技术精进,奈米制程也逐步缩小。就如前所述,网路越来越快,也因此需要更先进、更精密的晶片。这,就让台积电“纯代工”的优势逐渐显现。